Startup Atomera has had a rough ride since coming public last year, but its novel technology to improve semiconductors bears watching. By inserting a film of oxygen atoms in chips during manufacturing, the company promises to improve performance and reduce energy consumption of chips without the tremendous cost needed to move parts to the latest and greatest manufacturing process.

Atomera’s “MST” technology claims it can give existing chip-manufacturing nodes as much as a half- or a full-node shrink’s worth of improvement, alleviating much of the cost of actually going to a new node.

The notion of the End of Moore’s Law is debated — Intel refutes it — but it’s prompting lots of new ideas in chips. One approach is new chip designs, such as Alphabet’s (GOOGL) Google’s “Tensor Processing Unit,” a custom chip, something I explored in a recent article for Barron’s print magazine.

Another approach is to do more with what the chip world already has in its manufacturing kit.

I sat down recently with the management of one company doing the latter, called Atomera (ATOM).

Moore’s Law is “no longer a law in terms of the time frame” of improvement of chips, says Scott Bibaud, who took over as chief executive of Atomera in 2015. “In 2012, the cost per transistor for the first time did not go down,” he observes, an ominous sign for the industry.

“In the old days it was pretty clear what you would get from a node shrink, and now it’s no longer clear,” he says.

A node is chip-industry jargon for a change in the critical dimensions of transistors on a chip.

For example, most cutting-edge chips today are made in a 14-nanometer node, with the critical feature of the transistor measuring 14 billionths of a meter. That’s a reduction in size from the prior 20-nanometer node (though different chip makers will have slightly varying measurements.) All chip makers, including Intel and Taiwan Semiconductor Manufacturing (TSM), the largest contract chip maker in the world, serving individual “fabless” chip companies such as Qualcomm (QCOM), spend a considerable amount on R&D to move their parts from one node to another.

Atomera’s principle drive today is to license a set of technologies that will let companies do more with existing chip nodes, thus alleviating the immediate need to move every chip to the next-smallest node.

It’s been a rough ride for Bibaud and company in the stock market in the year since Atomera came public, with the shares dropping over 40% to a recent $4.42. Like some other intriguing tech firms, such as Pixelworks (PXLW), Atomera is a development-stage, pre-revenue company. It is working with four customers at the moment, whose names it cannot disclose, to evaluate the technology, hopefully leading to sales at some point.

Not helping the stock is that it has no coverage on the Street from the sell side.

Participating in the discussion I had was Bibaud, who was previously running the communications and broadcast chip division of Altera, which was bought by Intel; his CFO, Frank Laurencio,, who has a background at various tech companies and in tech investment banking; and CTO Robert Mears, who has authored hundreds of patents and publications, and who has a masters degree in physics from Oxford and a PhD in electronics and computer science from England’s University of Southampton.

It was Mears who originally founded the predecessor company, Nanovis, back in 2001, based on work in “nano-scale engineering.”

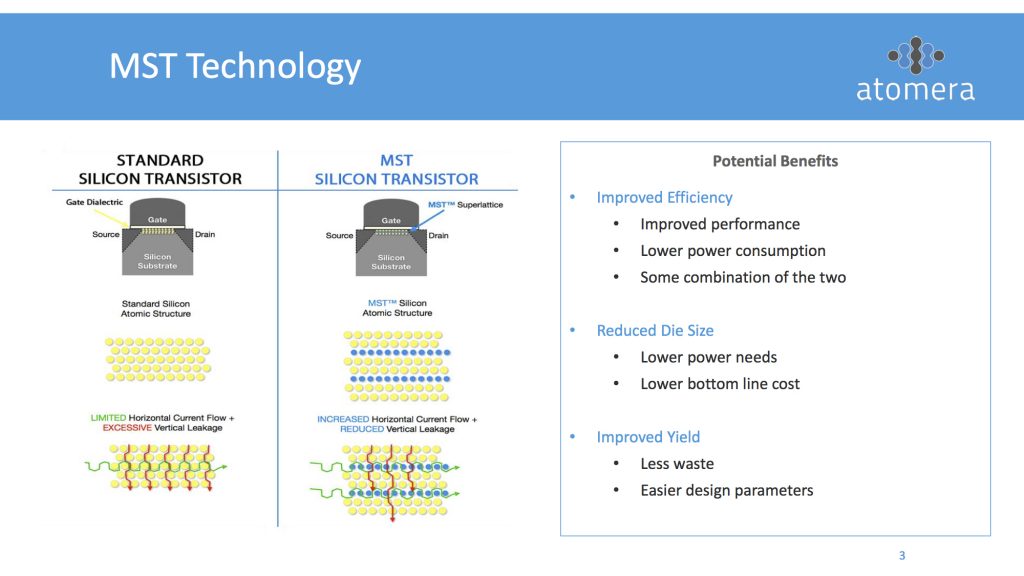

The key technology, called “Mears Silicon Technology,” or “MST,” is described by Bibaud as “a film that people put in an existing node that makes it perform significantly better.”

The approach consists of “carefully” placing oxygen atoms in the “channel region” that sits between the source and drain of a transistor, a process that is tricky, because “you can destroy the transistor” if you don’t do it right.

When done right, electrical current is improved in a silicon die, and leakage current is reduced, as depicted in the slide at the top of this post.

The result is to give a chip at any given node either improved performance, or lower power consumption, or some combination of the two, which is why most companies move down to smaller nodes.

That brings immediate benefits in things like the size of a chip. For example, “power management [chips], or anything with relatively high power, requires one to add a lot of circuitry,” says Bibaud. “If you lower the power requirement, you can do away with the oversize-wide transistors,” reducing the size of the device.

A further, bigger result is that chips can stay in older production nodes, rather than moving to the latest and greatest in order to get better performance and efficiency. And that can potentially save chip makers the big up-front expense of having to move to that next node.

Bibaud says his business is in line with trends in the industry of sticking with older technology for longer.

“The cutting edge nodes cost so much that people are talking about how to use legacy nodes,” says Bibaud.

“People are saying 28-nanometer will be useful for many years,” he adds. “And 40-nanometer chips are big in the world of automotive chips and for the Internet of Things.”

“We’ve even heard that the 130-nanometer node has the most new design starts of any node today for things like analog and sensor and power applications.”

Bibaud notes that a contract chip maker like TSM may have a 40-nanometer fab, or factory, say, that’s been running at capacity. Customers using that 40-nano process may be facing the choice of moving chips to 28-nano, but may not want to make the jump because of the cost of doing so.

DRAM makers, for example, could look to make improvements in their wares using conventional “2-D transistors” rather than bearing the expense of moving to the newer 3-D parts.

Because Atomera’s technology is a way to squeeze more out of existing chip technology, it is not the same as the equipment business dominated by Applied Materials (AMAT) and Lam Research (LRCX), says Bibaud.

“It’s outside the normal capex cycle,” says Bibaud. “And it is in a sense counter-cyclical: when people can’t afford to do major investments, this lets them boost up the performance of their existing equipment.”

In addition to helping with the older nodes, MST is applicable across any “geometry,” or node, says Bibaud, including “mainstream” ones such as 90-nanometer, 65-nanometer, or even 28-nanometer, and ultimately the most cutting-edge nodes as well.

Bibaud and Mears see the technology not only helping with costs, but also making possible some novel classes of devices in the case of cutting-edge nodes.

“This can have a big improvement in DDR [double-data-rate] DRAM for phones,” for instance. “You could produce an entirely new class of mobile DRAM, either making the DDR smaller, while maintaining the power levels, or keep them the same size and lower power consumption.”

During evaluation, potential customers determine what the performance improvement will be with the technology. “We can tell them maybe they will get 10% to 20% improvement, though it varies. It might be that, say, transistors will run 15% faster and with 8% less power draw. There’s a pretty wide range of performance improvements” that can be achieved.

Atomera has shown that there can be improvements of as much as 88% for a given node, “which is phenomenal,” says Bibaud. “Now, not everyone gets that, but probably, it has to be at least 15%” to justify the investment.

Atomera expects to ultimately make revenue off both licenses and royalties. There is a one-time license fee, then Atomera gets paid royalties based on volume of finished wafers shipped, or finished chip shipments in some cases.

The business is comparable to that of Tessera, which gets royalties on chip packaging (owned by Xperi(XPER)), he says, or that of Rambus (RMBS), the memory-chip technology licensor.

The chip makers “are very, very large,” he observes, “and we are a pretty small company, so we can charge a very modest royalty level, and stay lean and bring some very valuable IP because we can scale efficiently.”

But there’s a bit of a wait for actual sales, and Bibaud is not forecasting revenue at this point. With customers in an “evaluation phase,” it’s possible at any time they will decide they are ready to sign a license agreement with Atomera, he says. “We’re waiting for that first big breakthrough on the license business,” he says.

“It’s kind of like a drug development pipeline,” says Bibaud. “We are in the development stage” with the four customers, he says. In addition, the company has a partnership with chip tools maker Synopsys(SNPS), who integrates MST into its simulation modeling software for chip design. “The bulk who are testing are in leading analog chip” areas, he says.

“I don’t know if I can quantify the degree of confidence I have in their signing,” he says, “but they are spending a lot of money in evaluation, it’s quite expensive,” suggesting that they wouldn’t be doing so only to end up walking away.

Atomera, with just under 20 employees at the moment, is currently staffing up because “we’re bringing in a lot of new customers” in the evaluation stage.

“Our spending is not on staff but on expensive lease facilities to run this testing,” says Bibaud. He says Atomera is “very well capitalized,” with “almost three years of burn left” in terms of cash on hand. Cash and equivalents at the end of the June quarter was just under $22 million, according to the company’s 10-Q filing.

“So hopefully, we will be at revenue and cash flow before we have to raise anything further” in the capital markets, he says.

Mind you, the company filed a $30 million mixed securities shelf offering earlier this month, to allow it to sell shares if it chooses to at some point. Bibaud told analysts this month that the filing is “a tool used by virtually all public companies to efficiently position themselves for potential future fundraising.”

“As you can see from our financials, we are very well-positioned with over two years of cash in the bank and therefore have no near term plans to raise capital,” Bibaud said.